Продолжаем осваивать NGSPICE в целом и цифровую схемотехнику в частности.

Триггер (бистабильный мультивибратор) выполняет логическую функцию с обратной связью, в следствие которой имеет только два устойчивых состояния и способен под действием входных сигналов скачком переходить из одного устойчивого состояния в другое. Важной особенностью триггера как функционального устройства является способность оставаться в одном из двух состояний и по окончании действия переключающего сигнала. Приняв одно из состояний за «1», а другое за «0», можно считать, что триггер хранит (помнит) один разряд числа, записанного в двоичной форме и таким образом является элементарной битовой ячейкой для хранения двоичной информации. Такую память называют статической поскольку данные сохраняются только пока есть питание. При включении питания триггер с какой-то степенью вероятности принимает одно из двух возможных состояний и поэтому для первоначальной установки триггера в требуемое исходное состояние обычно предусматривается дополнительный механизм аппаратного сброса.

В следующих схемах для симуляции использовались SPICE модели логических вентилей: ИЛИ-НЕ | И-НЕ.

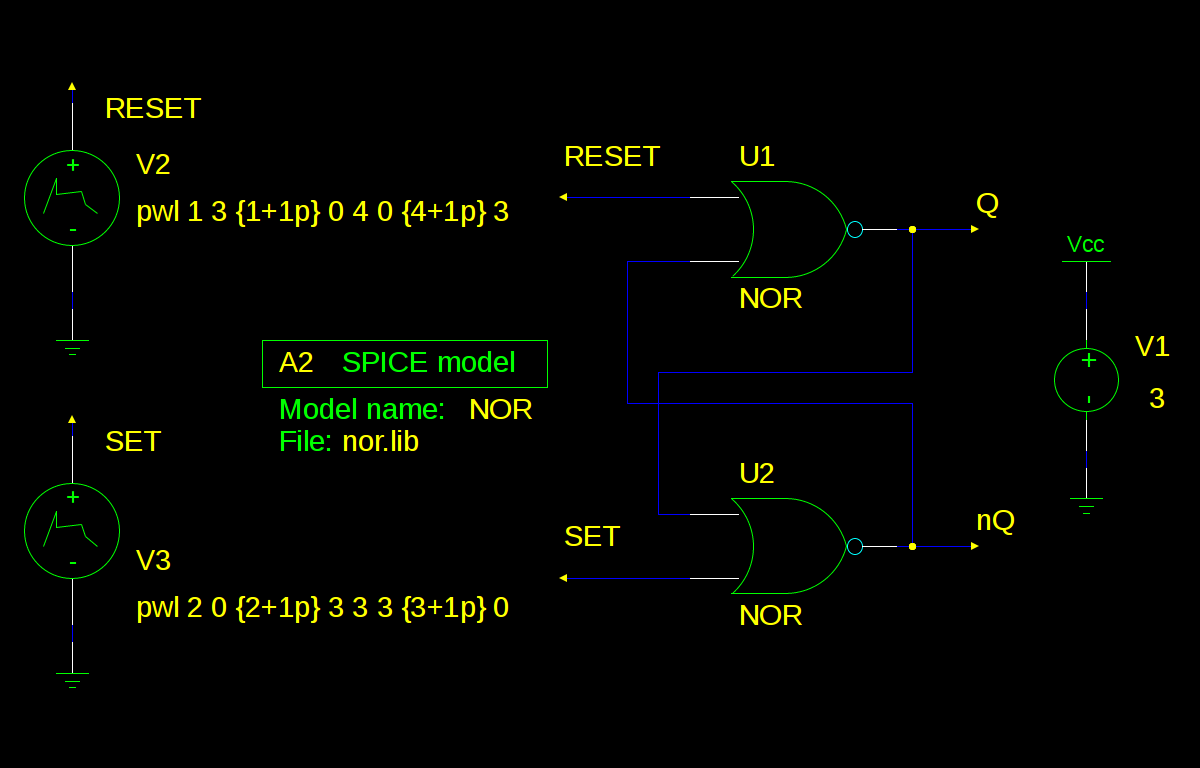

RS-триггер | netlist | ngspice.js

ngspice 1 -> source rs.net

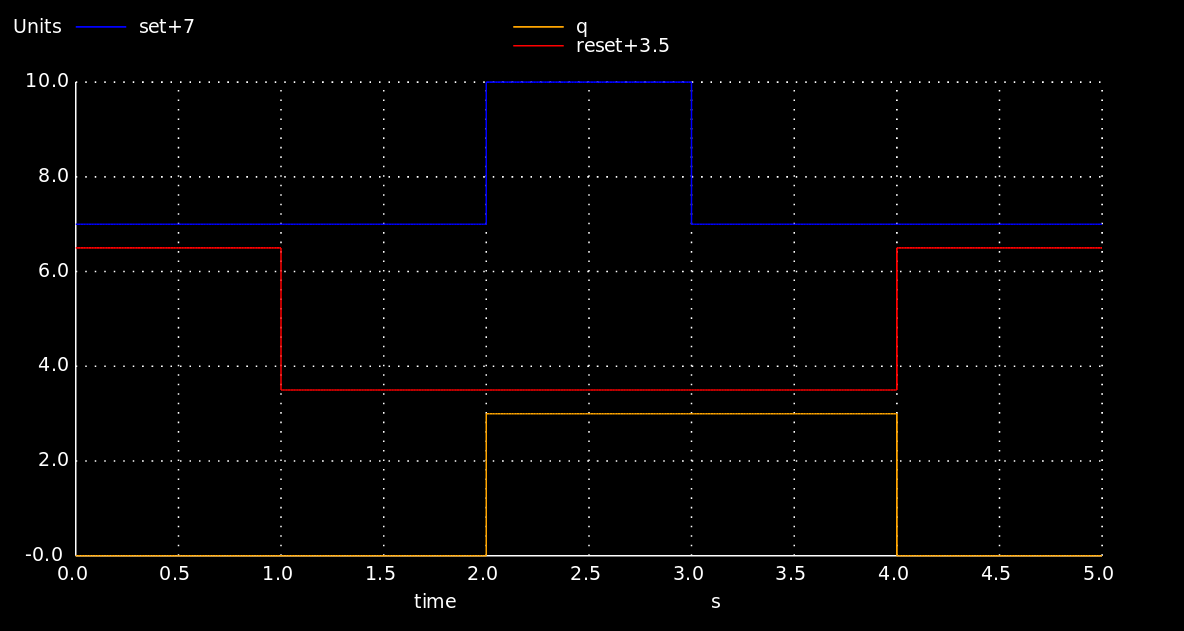

ngspice 2 -> tran 5m 5

ngspice 3 -> plot reset+3.5 set+7 q

RS-триггер является базовым при создании более сложных триггеров. В простейшем случае RS-триггер имеет два входа: S (Set) - вход установки триггера в единичное состояние, R (Reset) - вход установки триггера в нулевое состояние. В нормальном режиме выход nQ является инверсным по отношению к Q. Активный сигнал по входу S в момент появления (говорят по переднему фронту) заставляет выход Q перейти в единичное состояние. Активный сигнал по входу R переводит Q в нулевое состояние. При нулевом сигнале на обоих входах триггер хранит предыдущее состояние, а вот логика, при которой на оба входа R и S одновременно поданы логические единицы зависит от реализации RS-триггера - в приведенной схеме оба выхода перестают быть инверсными и переходят в состояние логического «0», однако данное состояние является неустойчивым и переходит в одно из устойчивых состояний при снятии управляющего сигнала с одного из входов.

RS-триггер, основанный на И-НЕ вентилях ведёт себя аналогично, только переключение происходит при логическом «0» на каком-либо из входов, а комбинация «0» на обоих входах порождает провалы в памяти. Избежать нежелательную логику позволяет нехитрый D-триггер:

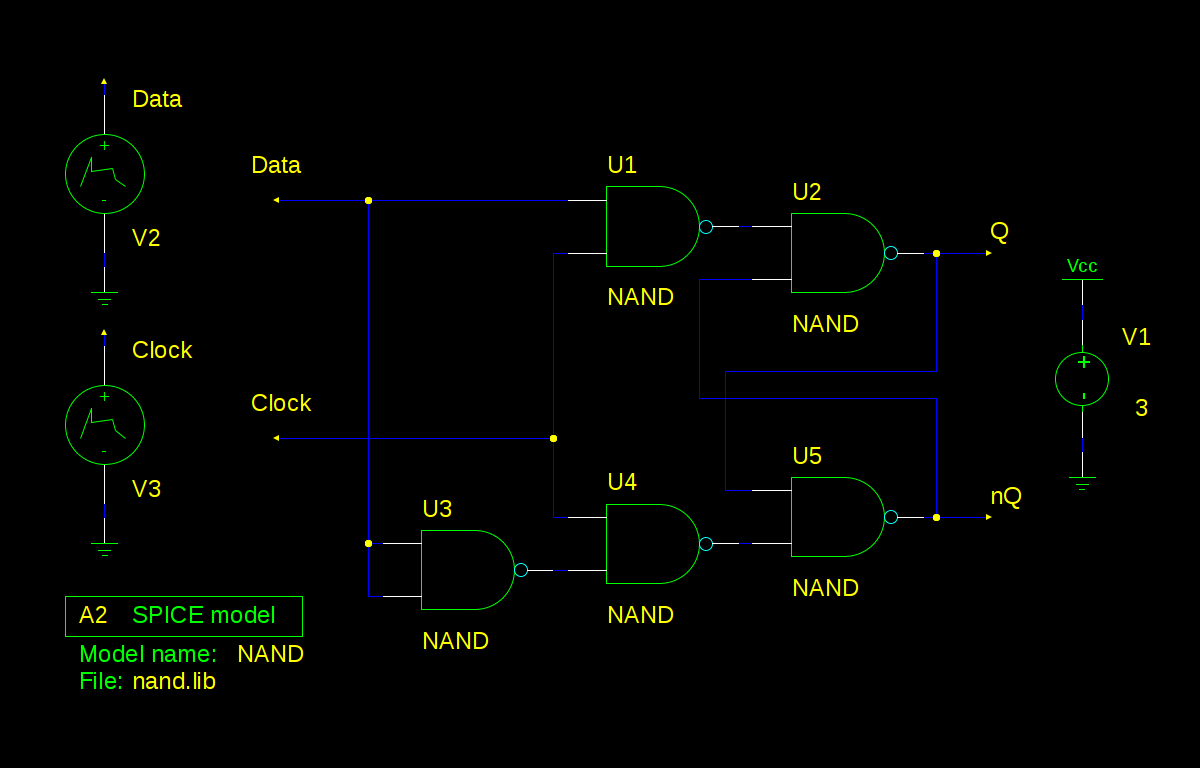

D-триггер | netlist | ngspice.js

ngspice 1 -> source d.net

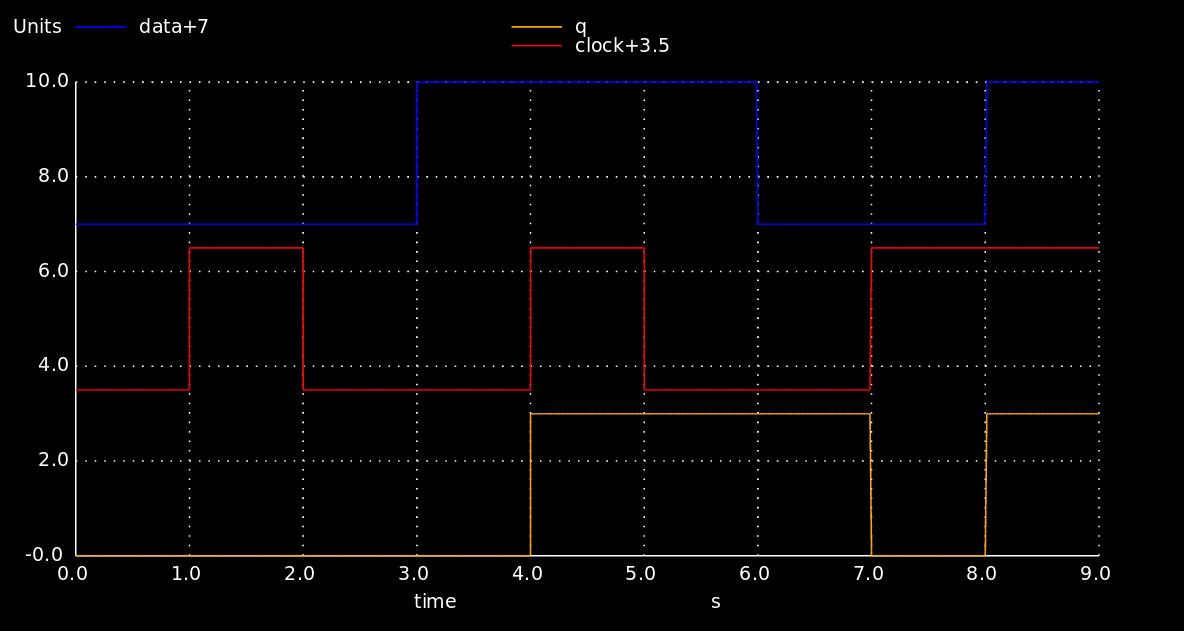

ngspice 2 -> tran 9m 9

ngspice 3 -> plot clock+3.5 data+7 q

В D-триггере бит данных поступает на информационный вход Data, а для осуществления записи данных необходимо подать импульс синхронизации Clock и поэтому подобные триггеры ещё называют тактируемыми (синхронными).

Приведенная схемы D-триггера также известна под названием «прозрачный фиксатор», т.к. выход Q насквозь просматривает (повторяет) информационный вход Data в течение интервала действия тактового сигнала (8 секунда на картинке). В некоторых случаях такая прозрачность нежелательна и тогда применяют двухступенчатые D-триггеры.

двухступенчатый D-триггер | netlist | ngspice.js

ngspice 1 -> source d-master-slave.net

ngspice 2 -> tran 10m 10

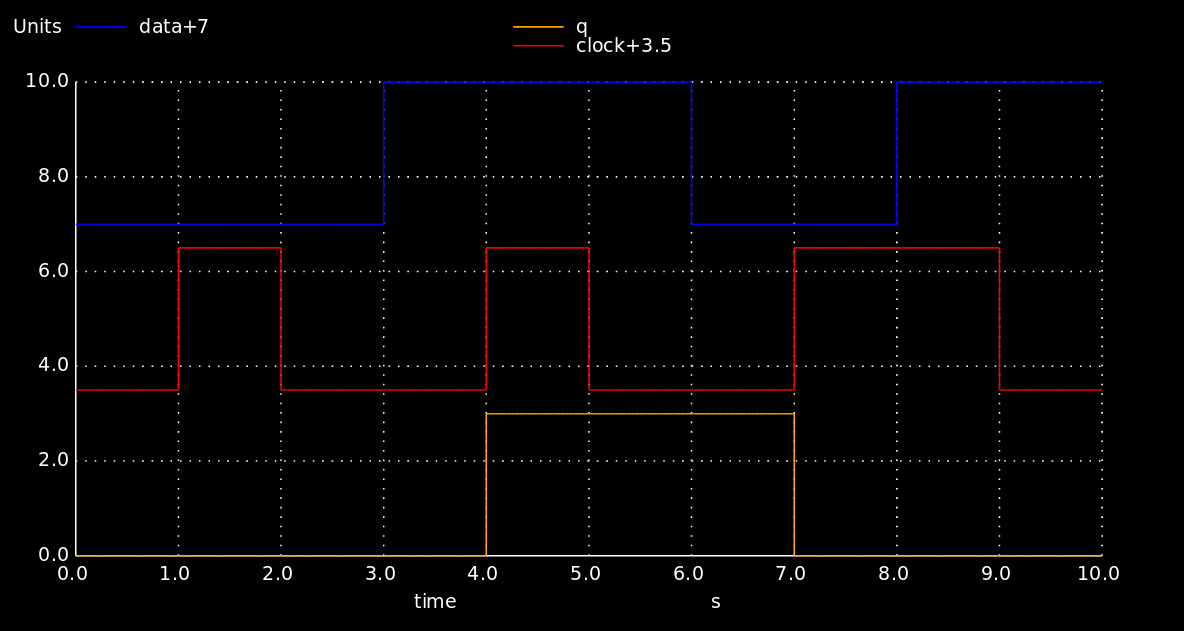

ngspice 3 -> plot clock+3.5 data+7 q

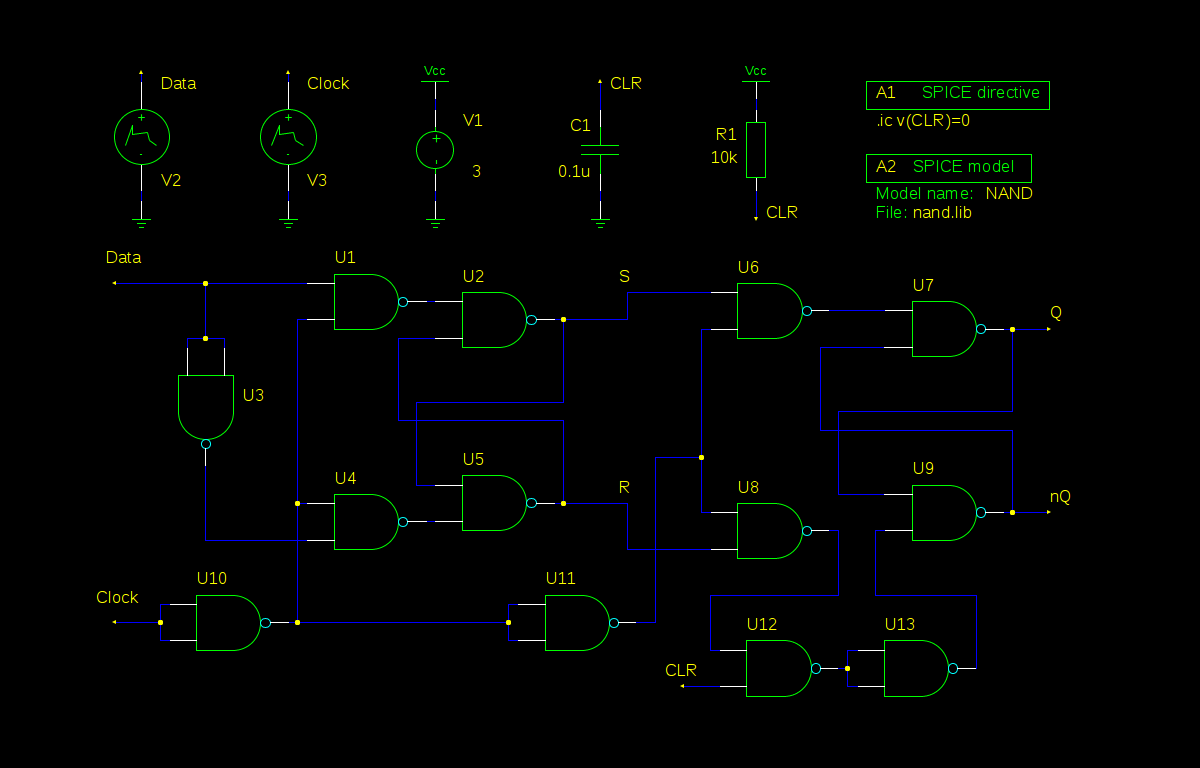

Двухступенчатый D-триггер состоит из двух синхронных триггеров - RS-триггера на вентилях U6-U9(при неактивном CLR выход U8 поступает на вход U9) и D-триггера на U1-U5. D-триггер является ведущим (master), а второй ведомым (slave).

При нуле на Clock ведущий триггер работает как «прозрачный фиксатор» и записывает/повторяет данные на входе Data, тогда как на ведомом отключён режим записи и он просто хранит своё предыдущее состояние. По переднему фронту на Clock теперь уже запись на ведущем отключена, он хранит своё предыдущее состояние, а ведомый в свою очередь копирует данные от ведущего. До тех пор пока на Clock продолжает действовать логическая единица уровень на Data не имеет значения (8 секунда на картинке). Что же произойдёт по заднему фронту Clock ? На картинке это 9 секунда, при этом на Data приходит уровень единицы. Выходит так что запись заблокируется на ведомом раньше, чем ведущий успеет переключиться.

Достаточно убрать инвертор U10 и двухступенчатый D-триггер начнёт переключаться только по заднему фронту Clock. Аппаратный сброс реализован на цепочке R1C1, а SPICE-директива (initial condition) .ic v(CLR)=0 явно указывает симулятору заряжать конденсатор честно. Без этой директивы в начальный момент симуляции конденсатор будет уже заряжен и логика RC сброса соответственно не отработает. Без аппаратного сброса до первой секунды на диаграмме после подачи питания на выходе можно было бы ожидать как логический «0» так и «1».

Далее цифровые счётчики.